# PCB schematic capture & layout best practices

Some tips to make life easier and your design more likely to work!

#### Schematic design

- There are two audiences for your schematic

- KiCAD

- A correct schematic will allow KiCAD to perform checks when you do layout

- E.g., is the ground pin on the IC physically wired to the circuit ground

- People

- To help debug, to instruct, to share

- We thus have two overall goals

- The schematic should be correct

- The schematic should be easy to read

This is just like for code

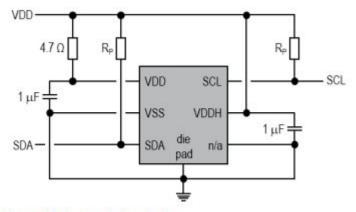

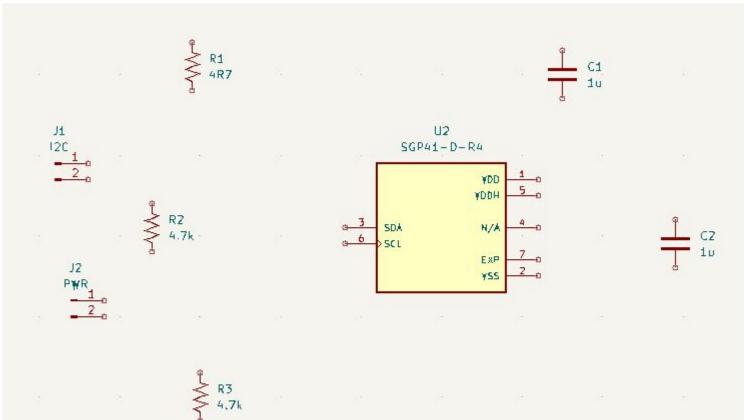

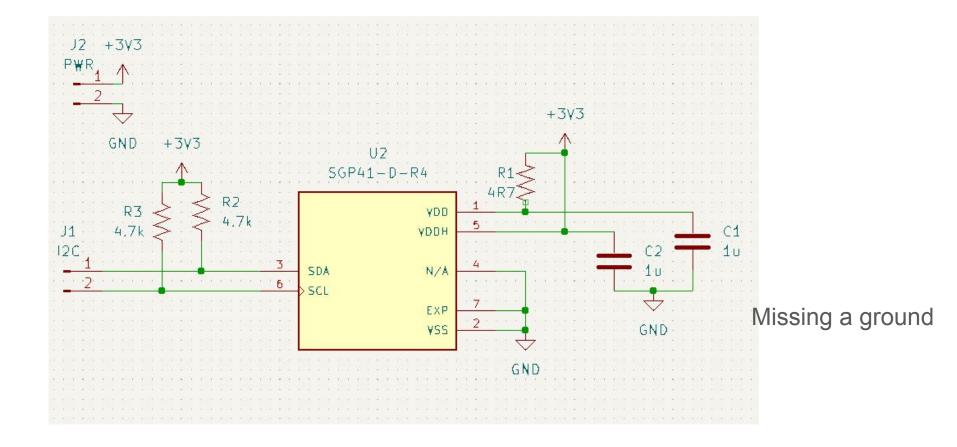

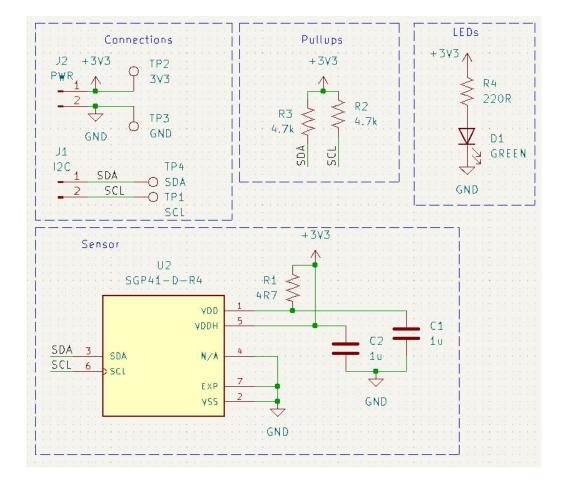

• Little board for an SGP41 VOC sensor

Figure 6 Typical application circuit.

#### Schematic design

- Use component designators

- $\circ$  Feel free to renumber starting at 1

- Add component values

- Label your connectors with something that makes sense

- $\circ \quad \ \ I2C \ vs \ Conn_01x_02Pin$

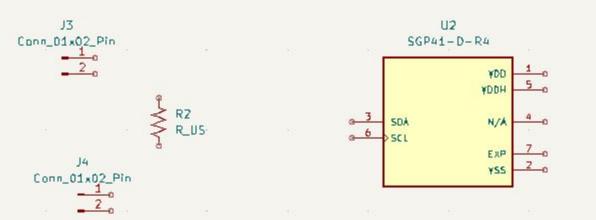

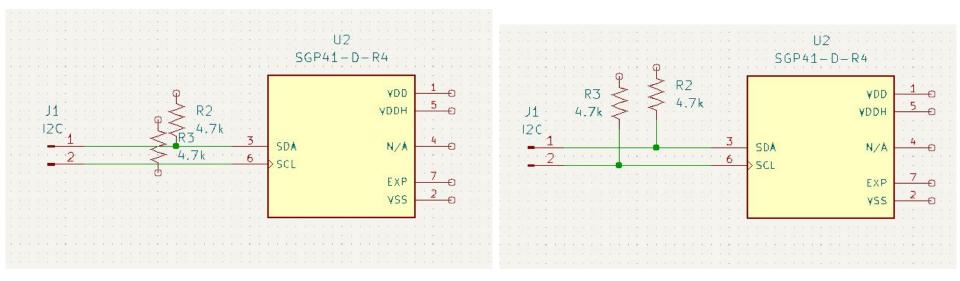

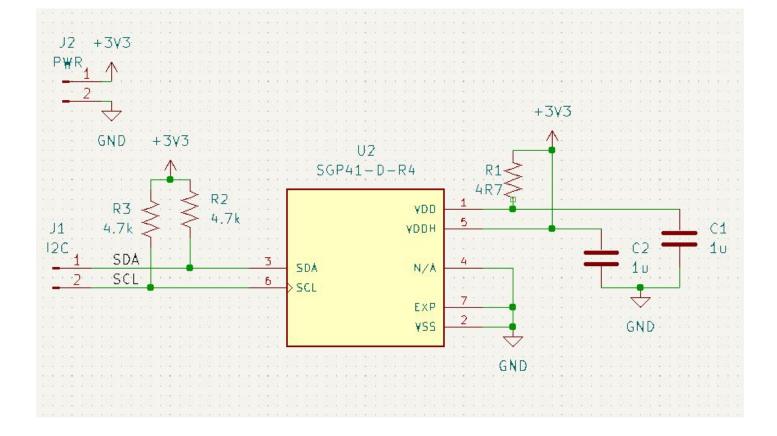

- R2 and R3 text is overlapping  $\rightarrow$  hard to read

- R3 is not actually connected to anything

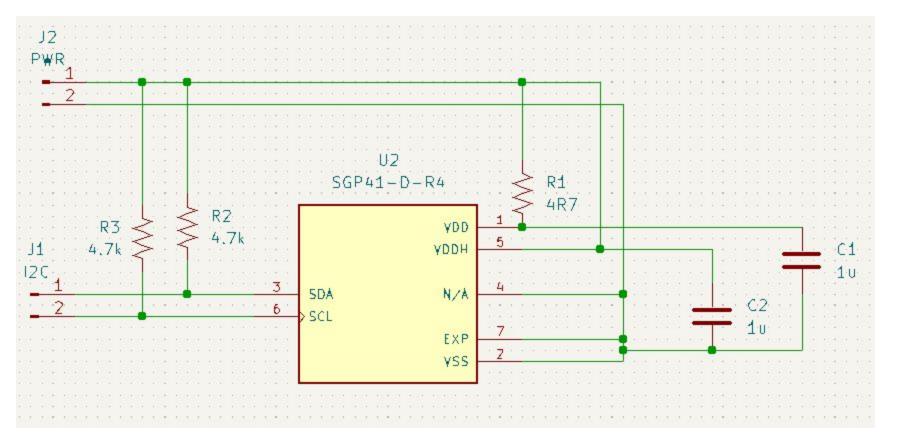

This is correct, but hard to read Lots of overlapping wires Hard to tell what's VDD, what's ground (VSS) by just looking

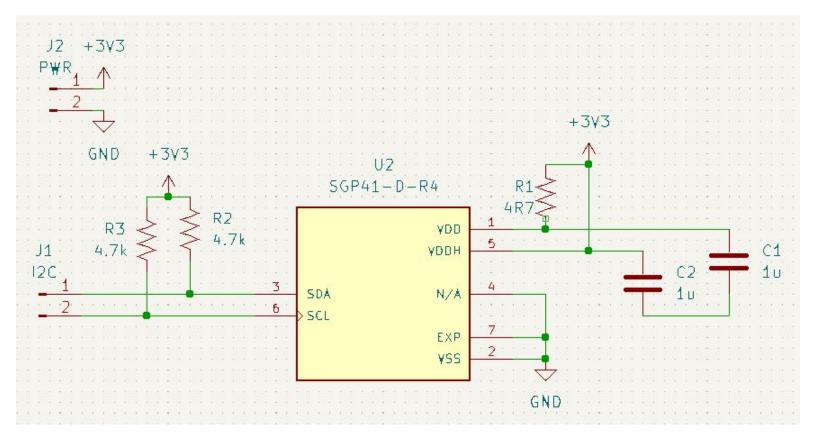

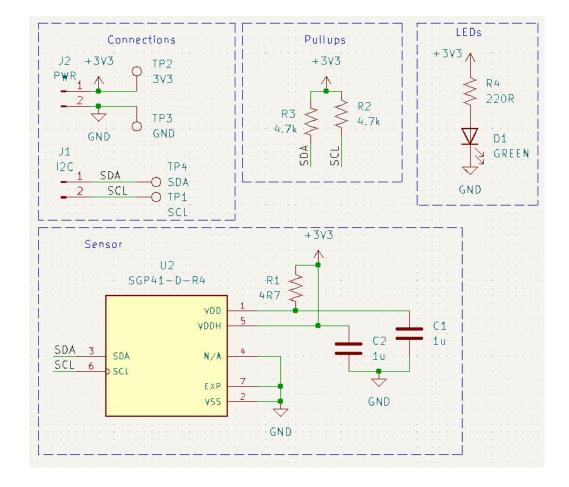

Better: Use GND and 3V3 power ports (P) Fewer crossing wires, easier to read Now I can see an error I made

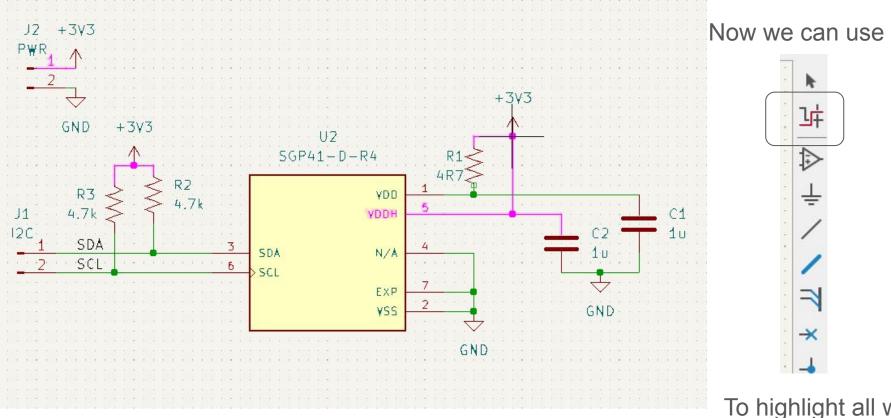

Assign SDA and SCL wires to SDA and SCL nets This will be really useful when we lay out the PCB Assign all important signals to nets

To highlight all wires of same net

Too far? I find this harder to read than the previous version

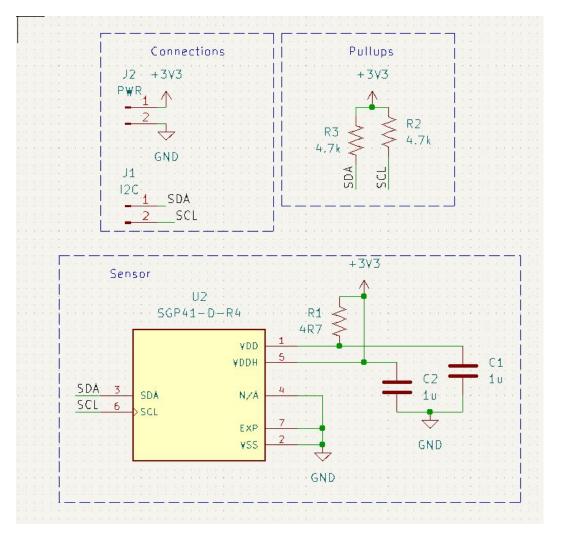

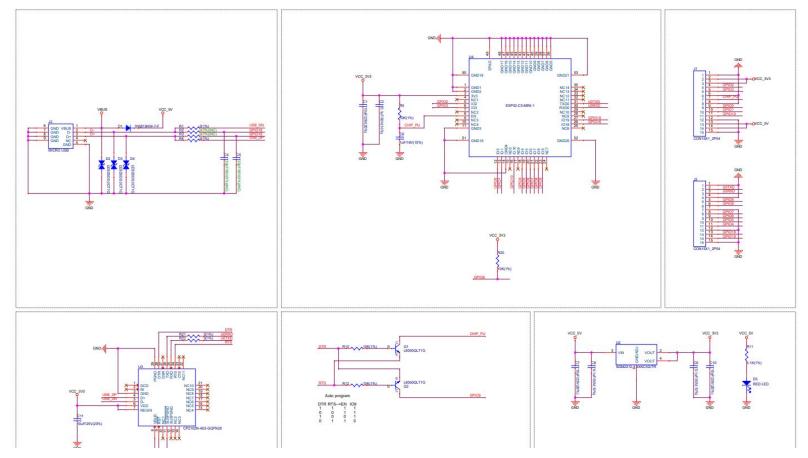

Balance use of direct connections with use of net labels This is part of the schematic for our ESP32C3 dev board See how they put different parts in different sections?

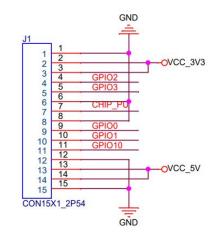

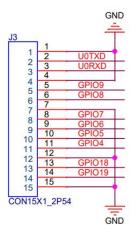

This is part of the schematic for our ESP32C3 dev board See how they put different parts in different sections? Net labels are useful for labeling the signals at all the connectors

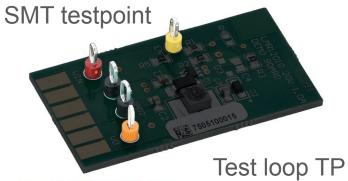

Don't forget about debugging! Here I've added 4 testpoints Make sure every important signal has a TP

Images from pcb.mit.edu

Image credit: TI, Editing credit: Winnie Szeto

I also added an LED so we know if the board is even powered

You can add LEDs for other signals Just be aware they may cost you power, which can be annoying for battery-powered systems

## You are not obligated to use any particular component or value

Example: many people put pull-up resistors on every board with I2C lines.

But your MCU may have internal pull-ups, or another board may have pull-ups on those lines already. You only need one set.

There is no problem to place components in the schematic and PCB but not install them in the actual board

## You are not obligated to use any particular component or value

Example: You spec a 220R resistor for your LED. But then you decide to use a 470R resistor to reduce power consumption. That's fine.

All that really matters is the footprint of the resistor on the PCB. If you place a 220R resistor with a 0805 footprint, you must use a 470R 0805 resistor.

That said, it's good idea to have the correct resistor values in your schematic because you will refer to that when assembling your board.

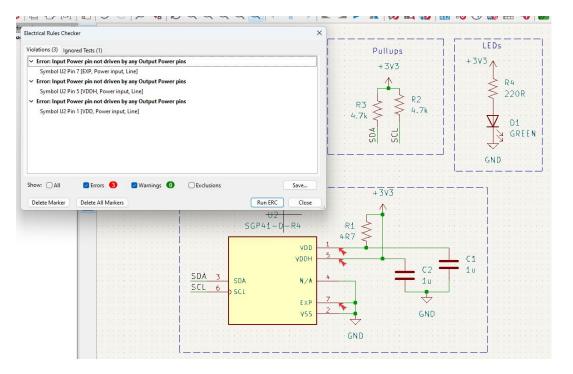

Always run and pass your ERC

Here KiCAD is upset because my IC has power and ground pins and they don't seem to be connected to a voltage source

|                                                                                  |                          | $\mathcal{F} \oplus \Theta \square$ |                     | (+ † •                                   | *                                 | C           |             |                                          | q   |

|----------------------------------------------------------------------------------|--------------------------|-------------------------------------|---------------------|------------------------------------------|-----------------------------------|-------------|-------------|------------------------------------------|-----|

| lectrical Rules Checker                                                          |                          |                                     |                     |                                          | ×                                 |             |             |                                          |     |

|                                                                                  |                          |                                     |                     |                                          | Г                                 | 1 252 1     |             | 1                                        | 1.1 |

| Violations (3) Ignored Tests (1)                                                 |                          |                                     |                     |                                          |                                   |             | P           | ullups                                   |     |

| <ul> <li>Error: Input Power pin not c<br/>Symbol U2 Pin 7 [EXP, Power</li> </ul> | Exclude this violation   |                                     |                     |                                          |                                   |             |             | 573                                      |     |

| ✓ Error: Input Power pin not c                                                   |                          | rning for all 'Input Po             | ower pin not driver | n by any Outpu                           | Power pir                         | s' violatio | ons         | NI                                       |     |

| Symbol U2 Pin 5 (VDDH, Po                                                        | Ignore all 'Input Power  | pin not driven by an                | y Output Power p    | ins' violations                          |                                   |             |             |                                          |     |

| <ul> <li>Error: Input Power pin not c</li> </ul>                                 | cult violation seventies |                                     |                     |                                          |                                   |             |             | 5                                        | F   |

| Symbol U2 Pin 1 [VDD, Powe                                                       | er input, Linej          |                                     |                     |                                          |                                   |             | 1.7k 5      | > 3                                      | - 4 |

|                                                                                  |                          |                                     |                     |                                          |                                   |             | ⊲           |                                          |     |

|                                                                                  |                          |                                     |                     |                                          |                                   |             | S D         | 20                                       |     |

|                                                                                  |                          |                                     |                     |                                          |                                   |             | 그 눈 그 눈 !!  | 10 10 10 10 10 10 10 10 10 10 10 10 10 1 |     |

|                                                                                  |                          |                                     |                     |                                          |                                   |             |             |                                          |     |

|                                                                                  |                          |                                     |                     |                                          | L                                 | · · · · ·   |             |                                          |     |

|                                                                                  |                          |                                     |                     |                                          |                                   | · · · · ·   | · · · · · · | · · · · ·                                |     |

| Show: 🗌 All 🛛 🔽 Errors                                                           | 3 Warnings 0             | Exclusions                          |                     | Save                                     |                                   |             |             |                                          |     |

|                                                                                  |                          | Exclusions                          |                     |                                          |                                   |             |             | 3v3                                      |     |

| Show: All Show: All Show: Celete Marker Delete All N                             |                          | Exclusions                          | Run I               |                                          |                                   |             |             | <u>3</u> γ <u>3</u>                      |     |

|                                                                                  |                          | Exclusions                          |                     | erc cia                                  |                                   |             | 4           | <u>3</u> γ <u>3</u>                      |     |

|                                                                                  |                          | Exclusions                          |                     | ERC Clo                                  |                                   | R1          | +           | <u>3</u> √3                              |     |

|                                                                                  |                          | Exclusions                          |                     | ERC CIA<br>U 2<br>L – D – R 4            | ise                               | R1<br>4R7   | +           | 3v3                                      |     |

|                                                                                  |                          | Exclusions                          |                     | ERC CIO<br>U2<br>L-D-R4<br>VI            | se                                |             | +           | 3v3                                      |     |

|                                                                                  |                          | Exclusions                          |                     | ERC CIA<br>U 2<br>L – D – R 4            | se                                |             | +           | 3v3                                      |     |

|                                                                                  |                          |                                     | SGP41               | erc cic<br>U2<br>L – D – R4<br>VI<br>VDI | изе<br>)р <u>1</u><br>)Н <u>5</u> |             | +           | 3v3                                      |     |

|                                                                                  |                          | SDA 3<br>SCL 6                      |                     | erc cic<br>U2<br>L – D – R4<br>VI<br>VDI | se                                |             | +           | 3v3                                      |     |

Always run and pass your ERC

Here KiCAD is upset because my IC has power and ground pins and they don't seem to be connected to a voltage source

But we know they are, so this is one error we can "Ignore all..."